ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject: Mathematics

# Study on Fundamental of Boolean and A\* Algebraic Relation with Logic Gates and Circuits

NIRVED KUMAR SHARMA<sup>1</sup> and Dr. DHARMENDRA SAXENA<sup>2</sup> 1-Research Scholar, Mansarovar Global University, Sehor (Bhopal) and 2- Professor, Mansarovar Global University, Sehor (Bhopal)

**DECLARATION::** I AS AN AUTHOR OF THIS PAPER / ARTICLE, HEREBY DECLARE THAT THE PAPER SUBMITTED BY ME FOR PUBLICATION IN THIS JOURNAL IS COMPLETELY MY OWN PREPARED PAPER.. I HAVE CHECKED MY PAPER THROUGH MY GUIDE/SUPERVISOR/EXPERT AND IF ANY ISSUE REGARDING COPYRIGHT/PATENT/ PLAGIARISM/ OTHER REAL AUTHOR ARISE, THE PUBLISHER WILL NOT BE LEGALLY RESPONSIBLE. . IF ANY OF SUCH MATTERS OCCUR PUBLISHER MAY REMOVE MY CONTENT FROM THE JOURNAL..

#### Abstract

This paper will likely to present the historical backdrop of rationale exchanging circuits. The exploration principally centers on the improvement of rationale and its application in the sequential request. Electronic and PC applications are a subset of this discipline. This is a paper about the essential necessities of rationale combination were momentarily inspected. Discuss a few fascinating facts as well as some design considerations. In relation to logic synthesis it also improves the depth of understanding of students. Comprehension of various logic functions and their minimization during a lecture, the technique is demonstrated, and it is then put into practice.

Before designing a logic gate, Boolean algebra or switching algebra is utilized to simplify Boolean equations and functions. Boolean algebra is a logic that allows you to do mathematical operations on binary integers, such as '0' and '1'. AND, OR, and NOT are the three basic operators of Boolean algebra. We are attempting to demonstrate these operations, as well as certain basic principles (commutative, associative, and distributive) and the related logic gate representations, in this work.

Keywords: Boolean algebra, mathematical operations, logic gates, circuit

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

#### 1. Introduction

At any given time, the output of a combinational circuit is determined by the circuit's current inputs. There is only one output for any possible combination of input variables.

There are no memory elements in combinational circuits, and there are no closed feedback loops. Input factors, yield factors, and rationale entryways are the fundamental worries of computerized circuits. The twofold provinces of Logic 1 and Logic 0 are utilized to address both info and result information. A combinatory consistent capacity with n input factors from an outer source and m result factors bound for an outside objective. As seen Fig. 1, m and n can theoretically be any positive integer

Figure: 1 Combinational logic circuit

There are 2n potential binary input values combinations for n number of input variables. m Boolean functions, one for each output, can be used to represent this circuit. This is the fundamental component of digital electronics. Today's world has been transformed into a digital

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

one based on this simple premise. The principal subjects of this outline review were time-series advancement history of rationale, portrayal of rationale, and different execution procedures.

## 2. Rationale to Digital Logic

The origins of digital logic circuits or digital systems can be traced back to philosophy. Modern digital systems are simply electrical implementations of logic. The nucleus of digital the system is a binary number system that Leibniz modified in the early 1700s [1]. Propositions and operations with logic Symbols began to be used to symbolize it, despite the fact that it had already been done. In the time of Aristotle, natural language was used to express the Francis Bacon (1561-1626), a fourth-century B.C. inventor, invented a "Bilateral alphabet code" was a binary scheme that used the letters A, B, and C. To create ciphers and codes, use the symbols A and B [2]. The Mitchell's introduction of indices into logic algebra is the Until date, the most effective method for representing logic propositions has been by using the letter [3] as a symbol This notion is extremely beneficial in In today's world, digital design propositions imply device inputs. A, B, C, D, E, F, G, H, I, J, K, L, M, N, O, P, Q, R sub scrip In 1854, George Boole combined arithmetic and logic. Contains two truth values: true or false, which is referred to as Boolean algebra is a type of algebra that is used to solve problems. The goal of these works was to create a model. Thinking, which might be conveyed using symbols and a diagram Through the use of a mechanical method of deduction based on rules, Algebraic equations are solved. The primary functions of The conjunction (AND), as well as the disjunction (OR), are used in Boolean algebra. His inventions include the conjunction (OR) and the negation (NOT). a 'NO' The entry "logic" already exists in his well-known book the In 1847, at page number 21, he published a mathematical explanation of logic [4]. These relationships were created to describe logical relationships. in the same way that addition, multiplication, and other mathematical operations are utilized in Numeric relationships are described using general algebra. Boolean algebra has played a crucial part in the advancement of science. In the field of digital electronics.

Boolean variable based math is streamlined and made more engaging by Charles Sanders Peirce. Cost makes sense of the major distinction between normal polynomial math and rationale variable based math. Cost makes sense of how images in like manner polynomial math are

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

utilized to mean items without making sense of them. for example in conventional polynomial math, records are clear and might be appointed any mathematical worth to get an outcome, however in the present rationale configuration, allocating x as information 1, y as info 2, and z as info 3 methods involving an alternate token for each information, and subsequently, the planner has no clue about what will occur on the off chance that the result isn't converted into a reasonable picture, and that implies utilizing one more token for yield. He looks at consistent files to token records and tracks down nothing. He utilized the qualities "v" and "f" to address valid and bogus qualities, individually. "The overall rationale is that the assertion is either obvious or bogus, and no further qualification is perceived," Charles adds. As the geometer says, this is a clear term. The metric idea is that all confidence is pretty much misleading and the inquiry is one of the sets. He takes on the past view that there are two kinds of rationale, valid and bogus. For v and f, Boole picked 1 and 0, separately.

In digital electronics, logic high and logic low are used interchangeably to represent high reference voltage or extremely close to high reference voltage and low reference voltage or very close to low reference voltage values with the same notation. Peirce suggested a method of presenting any proposition that is either true or untrue. Before Peirce, any statement x was expressed as (v-x) or x if it was true; otherwise, it was written as (x-f) or x if it was false (1-x). He uses a new writing style in which only x represents the true value of the proposition and y represents the false value. Peirce redefined propositional logic and presented it as icons in his renowned paper "On the Algebra of Logic: A Contribution to the Philosophy of Notation." The identity formula  $(x \ x)$  is featured in the first icon of algebra. He uses the sign " to symbolize comparable to suggests (). The second type of hypothetical inference icon, modus ponens, is used to signify "if x, then y  $(y \ x)$ ". The third icon represents the principle of the copula's transitiveness, often known as the syllogism principle in Barbar or the chain of consequence.

According to this, if y follows from x and z follows from y, then z follows from x, symbolically  $(x \ y) (y \ z)$  then x z. The fourth kind's emblem is modus tollens, which is used for negation. The negation of the modus ponens proposition is the modus tollens proposition. He uses this icon to prove that the second icon's negation of y proposition x is also false. The idea of excluded

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

middle and various pro-positions associated with it are represented by a fifth icon. OR logic is represented by the '+' symbol, while AND logic is represented by simple multiplication [3]. Mitchell's notation for some () and all () was also extended by Peirce. He recommends that for an aggregate, the capacity is valid if no less than one individuals is valid, and for an item, the capacity is valid assuming every one of the people are valid. These two images have been utilized to represent. SOP and POS with a similar significance till now.

## 3. Logic Implementation

The first logic demonstration machine, known as the "Demonstrator," was designed by Charles Stanhope and was capable of solving both traditional and numerical syllogisms mechanically [7]. Allan Marquand and Prof. Rockwood built the 'Logical Machine' in 1881-1882. Prof. Jevons and Prof. Venn's machines are comparable, but this one is more advanced. The Logic Machine could deal with four sources of info and could be extended to deal with quite a few information sources. The Logic Machine is the world's most memorable completely working mechanical gadget for a broadly useful truth practical rationale processor that shows every one of a consistent recommendation's genuine ramifications in an orderly way [5]. In a letter to Marquand in 1886, Charles Sanders Peirce portrayed how consistent tasks might be finished utilizing just electrical exchanging circuits. Charles shows two fundamental electrical circuits in which all switches are equal and series, taking into account sensible increase (ANDing) and coherent expansion (ORing) [8].

Price and Marquand used electromagnetic switching circuits to augment the Logic Machine in 1890 [9]. The AND function was used in the 1891 Strowger switching circuit based on electromagnetic relay [10]. The earliest electromagnetic sequential circuit is the Strowger relay switch, which operates in a step-by-step manner in a specific sequence.

In 1907, Lee De Forest proposed that AND logic be implemented using a modified Fleming valve. Walter Bothe received a portion of the Nobel Prize in Physics in 1954 for inventing the coincidence circuit, the first modern electronic AND gate in 1924. For his computer Z1 (from 1935 to 1938), Konrad Zuse created electromechanical logic gates [11].

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject: Mathematics

# 4. Switching Circuit Synthesis

In 1936, Claude E. Shannon pioneered the utility of Boolean algebra to the take a look at and layout of switching circuits. A switching feature is represented via way of means of X and its terminal via way of means of a, b in Shannon's diagram. He applied the symbols Xab to symbolize circuit, 0 (zero) to symbolize the issue of a closed circuit, and 1 (unity) to symbolize the issue of an open circuit, that are all very much like the Calculus of Propositions used withinside the symbolic take a look at of good judgment. He uses '+' for every collection connection (ANDing operation) and '•' for every parallel connection (ORing operation) of transfer switching elements. He located an analogy among Boolean algebra and switching systems. For symbolic good judgment, he correctly correlates De Morgan's low and Huntington's postulates with the switching feature. He additionally efficaciously simplifies switching circuits the use of good judgment algebra and identifies a hard and fast of good judgment formulation which are nevertheless beneficial for minimizing complicated logical circuits [12]. Price representation, i.e. '•' for every collection connection and '+' for every parallel connection of transfer switching elements, remains used today. The open circuit is represented via way of means of the image 0 (zero), while the near circuit is represented via way of means of the image 1 (unity), that is the polar contrary of Shannon's representation. All symbolic analyses are nevertheless possible because of the good judgment's duality principle.

In logic circuit synthesis, symbolic analysis of switching circuits is crucial. His research shifted people's perceptions of digital systems. In November 1937, Bell Labs' George Stibitz built the ModelK, a relay-based computer that calculated via binary addition [13].

## 5. Representation Techniques

Logic gates can be used to execute any logical expression.

English letters are used to identify input variables. The value of any input variable without negation (1) or with negation (0) but not both, as well as the symbolic representation of that variable, is referred to as literal. A combinational circuit can be described or depicted in five different ways.

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject: Mathematics

## **5.1** Algebraic forms

The most frequently used algebraic forms are canonical explanations of logic assertions. Because there are only a few terms at which the function is changed, The sum of products (SOP) is a very efficient representation of any switching function. Check:

$$Y = \bar{A}\bar{B}\bar{C} + A\bar{B}\bar{C} + A\bar{B}\bar{C} + AB\bar{C} + ABC. \tag{1}$$

$$Y = \bar{B}\bar{C} + AB. \tag{2}$$

$$\bar{Y} = (B+C)(\bar{A}+C)(\bar{A}+\bar{B}). \tag{3}$$

Expression (1) is the regular SOP format, expression (2) is the minimized SOP format, expression (3) is the same expression in POS format, and A, B, and C are three Boolean input conditions. Only the complement is represented by a bar.

#### **5.2 Tabulated forms**

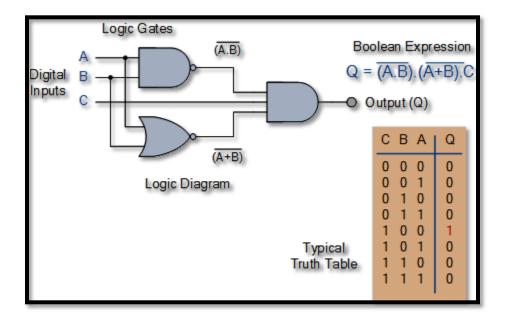

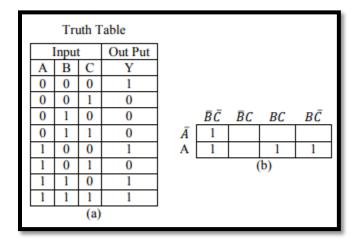

The input combinations for which the outputs become logic high, logic low, or in the don't care state are enumerated. The K-map approach is useful for logic minimization as well as tabular input [14]. Figure 2(a) shows the truth table and Figure 2(b) shows the KMap representation of the equation (1).

Fig 2: Tabular representation (a) Truth table (b) K-Map

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

## 5.3 Graphical forms

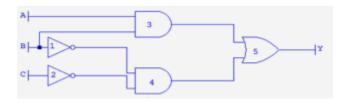

Other representation strategies include graphical representations such as logic networks. Basic logic gate logic networks can be represented using simple logic gates. Figure 3 illustrates equation (2). Using two inverters, two AND gates, and one OR gate, the circuit obtained from equation (1) after minimization.

Fig 3: Graphical representation method.

## **6. Minimization Techniques**

It is necessary to realize logic expression conversion in electrical switching circuits during design. Mapping and minimization are two important strategies for reducing a combinational logic expression and a logic diagram to the smallest possible number of parts.

For the same logic function, several combinational circuits can be used to produce the proper output response for all input values, which is referred to as a functionally equivalent circuit [16].

The best implementation is determined by the design goals and criteria, which include area analysis, the number of gates, the number of gate inputs and outputs, and so on. Implementations with simplification have the following benefits: lower costs, fewer logic gates, lower complexity, simpler circuit, and shorter latency [17]. The difference between the gate output and the input load factors to which that gate output is attached is known as the fan-out factor. Many input gates required more space, and the connections between the gates expanded, making the design more complex. The entire area of both the gate and the interconnection determines the area or size.

Area minimization is also important in design.

As the number of gates in the longest path from input to output, i.e. the number of levels, increases, so does the inherent and extrinsic delay. Combinational circuits with arbitrary finite

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

gate and wire delays are also taken into consideration during the design process. Because the output does not vary monotonically during the input transition, there is no suitable implementation when designing with random gate and wire delay [18]. The maximum delay calculated for all potential data flow paths and glitches should be kept as low as feasible.

Combinational logic circuits are always dependent on the current combination of inputs and map to a single output for each combination of inputs [19].

To get the desired single output in a multilevel combinational logic circuit, the time-dependent relationships must be carefully and explicitly coordinated.

Multilevel logic network implementation frequently It requires fewer gates and connections than a two-level logical network, but the design approach is more difficult [20] [21].

Both static and dynamic power dissipation increase as the number of gates increases. When gates remain in the same condition, static power dissipates. Dynamic power consumption is usually expressed as a function of frequency and is proportional to the rate at which the logic input changes. The faster the logic input changes, the greater the dynamic power loss [22].

The number of reduced term terms and the number of phrase literals are related to the cost of implementing the hardware and implementing the formula.

## 7. Conclusion

This paper provides a current state-of-the-art review of logic synthesis. Different representation strategies were required for different minimization techniques and switching circuit implementation. This research looked at various minimizing techniques and processes. The problem of logic minimization is not new, yet it hasn't died yet. It is used in various areas of VLSI synthesis, switching system design, built-in self-test, and many more applications.

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject: Mathematics

#### 8. References

- [1] N. Balabanian and B. Carlson, Digital logic design principles, John Wiley, pp- 39-40, 2001.

- [2] J. A. Camara, Electrical and Electronics reference manual for the electrical and computer PE exam, 2010.

- [3] J. Gregg, Ones and zeros: Understanding Boolean algebra, digital circuits, and the logic of sets, Wiley- IEEE press, 1998.

- [4] D. E. Muller, Application of Boolean algebra to switching circuit design and to error detection, Transactions of the IRE professional group on electronic computers,pp- 6-12, 1954.

- [5] W. Millan, A. Clark, Ed dawson, Heuristic design of cryptographically strong balanced Boolean functions, International Conference on the theory and applications of cryptographic techniques, pp- 489-499, 1998.

- [6] G. L. Snider, A. O. Orlov, I. Amlani, G. H. Bernstenin, C. S. Lent, J.L. Merz, W. Porod, Quantum- dot cellular automata: Line and majority logic gate, Japanese journal of Applied physics, Vol. 38, No12, 1999.

- [7] Computer Museum. Computer museum of America. Available at http://history compuer.com/Modern Computer/thinkers/Stanhope.html last seen July (2015).

- [8] Peirce, Charles Sanders. "Writings of Charles S. Peirce: 1857-1866" (1982) vol. 1. Indian a University Press.

- [9] Computer Museum. Computer museum of America. http://historycomputer.com/ModernComputer/thinkers/Peirce.html last seen (July 2015).

- [10] Almond B. Stronger, Automatic telephone-exchange. U.S. Patent No. 447,918. 10 Mar. (1891)

- . [11] Jess, Jochen AG. "Designing electronic engines with electronic engines: 40 years of bootstrapping of a technology upon itself." in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, (2000) Vol.19 No.12, 1404-1427.

ISSN: 2320-3714 Volume: 2 Issue: 2 May 2022 Impact Factor: 5.7 Subject Mathematics

- [12] C.E. Shannon, "A symbolic analysis of relay and switching circuits," in Trans. of the American Institute of Electrical Engineers, (1938) Vol. 57, No. 12, 713-723.

- [13] M. M. Irvine, "Early Digital Computers at Bell Telephone Laboratories." in IEEE Annals of the History of Computing, (2001), Vol.23 No. 3, 22-42.

- [14] Karnaugh, M., "The map method for synthesis of combinational logic circuits," Transactions of the Communication and Electronics, American Institute of Electrical Engineers, Part I: Nov. (1953), Vol.72, No.5, 593-599.

- [15] F. Dartu, N. Menezes, J. Qian, L.T. Pillage, "A gatedelay model for high-speed CMOS circuits," Proc. ACM. 31st annual Design Automation Conference (DAC '94), June (1994) 576-580. doi:10.1145/196244.196562.

- [16] Y. Matsunaga, "An efficient equivalence checker for combinational circuits," Proceedings of the 33rd annual Design Automation Conference, DAC '96 (1996),629- 634.doi: 10.1109/DAC.1996.545651.

- [17] S. Roy and C.T. Bhunia, "Constraints Analysis for Minimization of Multiple Inputs Logic Programming," in Elsevier Proc. of International Conference on Signal and Speech Processing (ICSSP-14), Aug. (2014), 61-64, Kollam, India

- [18] K. P. Parker and E. J. McCluskey, "Probabilistic treatment of general combinational networks," IEEE Trans. Computers, June (1975), vol. C-24, 668-670.

- [19] K. Fant and S.A. Brandt, "Null Conventional Logic: A Complete and Consistent Logic for Asynchronous Digital Circuit Synthesis," Proc. Int'l Conf. Application Specific Systems, Architectures and Processors (ASAP 96), IEEE CS Press, (1996) Los Alamitos, Calif. 261-273.

- [20] S.M. Nowick and D.L. Dill. "Exact two-level minimization of hazard-free logic with multiple-input changes," IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, (1995), vol. 14, no. 8, 986-997.